Flip-Flop atau latch merupakan sirkuit elektronik yang memiliki dua arus stabil dan dapat digunakan untuk menyimpan informasi. Sebuah flip-flop merupakan multivibrator-dwistabil Sirkuit dapat dibuat untuk mengubah arus dengan sinyal yang dimasukkan pada satu atau lebih input kontrol dan akan memiliki satu atau dua output. Ini merupakan elemen penyimpanan dasar pada Logika Sekuensial.

Flip-flop dan latch merupakan bangunan penting dalam

sistem elektronik digital yang digunakan pada komputer, komunikasi dan tipe

lain dari sistem. Flip-flop dan latch digunakan sebagai elemen penyimpan data,

seperti penyimpan data yang dapat digunakan untuk menyimpan memori, seperti

sirkuit yang dijelaskan pada logika sekuensial. Flip-flops juga dapat digunakan

untuk menghitung detak, dan untuk mengsinkronisasikan input signal waktu

variable untuk beberapa signal waktu yang direferensi. Flip-flop dan latch

digunakan sebagai elemen penyimpanan data.Penyimpanan data ini digunakan untuk

menyimpan state (keadaan) pada ilmu komputer, dan sirkuit ini merupakan logika sekuensial.

Sirkuit juga dapat digunakan untuk menghitung bunyi teratur dan sinkronisasi

sinyal.

Rangkaian Flip flop adalah rangkaian digital yang

digunakan untuk menyimpan satu bit secara semi permanen sampai ada suatu

perintah untuk menghapus atau mengganti isi dari bit yang disimpan. Prinsip

dasar dari flip-flop adalah suatu komponen elektronika dasar seperti

transistor, resistor dan dioda yang di rangkai menjadi suatu gerbang logika

yang dapat bekerja secara sekuensial. Nama lain dari flip-flop adalah

multivibrator bistabil.

Multivibrator adalah suatu rangkaian regeneratif

dengan dua buah piranti aktif, yang dirancang sedemikian sehingga salah satu

piranti bersifat menghantar pada saat piranti lain terpancung.

Macam-macam flip-flop :

1.)

RS flip-flop

Flip-flop RS atau SR (Set-Reset) merupakan dasar dari

flip-flop jenis lain.Flip-flop ini mempunyai 2 masukan: satu disebut S (SET)

yang dipakai untuk menyetel (membuat keluaran flipflop berkeadaan 1) dan yang

lain disebut R (RESET) yang dipakai untuk me-reset (membuat keluaran berkeadaan

0). Flipflop RS dapat dibentuk dari dua gerbang NOR atau dua gerbang NAND.

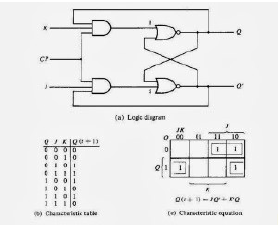

2.) JK flip-flop

Flip-flop JK yang diberi nama berdasarkan nama

masukannya, yaitu J dan K. Flip-flop ini mengatasi kelemahan flip-flop RS, yang

tidak mengizinkan pemberian masukan R=S= 1, dengan meng-AND-kan masukan dari

luar dengan keluaran.

Flip-flop JK ini bekerja tak serempak. Untuk

memperoleh flip-flop JK yang dapat bekerja serempak dengan rangkaian lain perlu

ditambahkan kelengkapan untuk penabuhan (clocking). Ini dapat dilakukan dengan

meng-AND-kan pulsa CP (clock Pulse) dengan masukan K dan J seperti yang

ditunjukkan pada Gambar 6.8. Perlu dicatat bahwa untuk flip-flop yang peka

terhadap perubahan pulsa negatif, pada masukan CP diberikan lingkaran kecil

seperti pada NOR dan NAND.

3.) D flip-flop

Nama flip-flop ini berasal dari Delay. Flip-flop ini

mempunyai hanya satu masukan, yaitu D. Jenis flip-flop ini sangat banyak

dipakai sebagai sel memori dalam komputer. Pada umumnya flipflop ini dilengkapi

masukan penabuh.

Dapat dilihat bahwa sebenarnya flip-flop D berfungsi

seperti apa yang dilakukan oleh flipflop JK bila masukan masukan K dihubungkan

dengan komplemen masukan J.

4.) T flip-flop

Nama flip-flop T diambil dari sifatnya yang selalu

berubah keadaan setiap ada sinyal pemicu (trigger) pada masukannya. Input T

merupakan satu-satunya masukan yang ada pada flip-flop jenis ini sedangkan

keluarannya tetap dua, seperti semua flip-flop pada umumnya.

Kalau keadaan keluaran flip-flop 0, maka setelah

adanya sinyal pemicu keadaan-berikut menjadi 1 dan bila keadaannya 1, maka

setelah adanya pemicuan keadaannya berubah menjadi 0. Karena sifat ini sering

juga flip-flop ini disebut sebagai flip-flop toggle (berasal dari skalar

toggle/pasak). Flip-flop T dapat disusun dari satu flip-flop RS dan dua gerbang

AND.

5.) CRS

flip-flop

RS Flip-flop adalah clocked RS-FF yang dilengkapi

dengan sebuah terminal pulsa clock. Pulsa clock ini berfungsi mengatur

keadaan Set dan Reset. Bila pulsa clock berlogik 0, maka perubahan logik pada

input R dan S tidak akan mengakibatkan perubahan pada output Q dan Qnot. AkanÂ

tetapi apabila pulsa clock berlogik 1, maka perubahan pada input R dan S dapat

mengakibatkan perubahan pada output QÂ dan Q not.

Prinsip kerja

Flip-flop:

- Jika clock bernilai rendah (0) maka flip-flop J-K master akan tidak aktif, tetapi karena input clock flip-flop J-K slave merupakan komplemen dari clock flip-flop master maka flip-flop slave menjadi aktif, dan outputnya mengikuti output flip-flop J-K master.

- Jika clock bernilai tinggi (1), flip-flop master aktif sehinga outputnya tergantung pada input J dan K, pada sisi lain flip-flop slave menjadi tidak aktif karena clock pemicunya bernilai rendah (0).

- Pada saat sinyal detak berada pada tingkat tinggi, master-nya yang aktif dan slave-nya tidak aktif.

- Pada saat sinyal detak berada pada tingkat rendah, master-nya yang tidak aktif dan slave-nya yang aktif.

- Jika input J diberikan bersama-sama dengan tepi naik pulsa pemicu, flip-flop master akan bekerja terlebih dahulu memantapkan inputnya selama munculnya tepi naik sampai clock bernilai rendah (0).

- Setelah clock bernilai rendah (0),flip-flop master akan tidak aktif dan flip-flop slave bekerja menstransfer keadaan output flip-flopmaster keoutput flip-flop slave yang merupakan output flip-flop secara keseluruhan.

0 komentar:

Posting Komentar

SILAHKAN TINGGALKAN KOMENTAR